Working principle

Under normal circumstances, the memory refresh circuit must refresh the DRAM once within a few milliseconds (ms), otherwise the data will be lost. Much like a quicksand funnel, once no sand is added, it will leak completely.

In the standard PC circuit design, DRAM is charged once every 15 microseconds (us), and the entire charging operation must be completed within 4ms.

Development and changes

In recent years, due to the faster and faster CPU speed, DRAM has become less and less able to keep up with the speed of the CPU, making the matching relationship between the two out of balance. This makes the CPU overkill and has to stop and insert a few wait cycles to match the slow memory brush

new speed. Therefore, the interleave (Interleave) method of refreshing the memory on the motherboard of the AT era was born. This design requires at least two BANKs. When one bank exchanges data with the CPU, the other bank takes the opportunity to refresh the data. Refresh work in a leisurely manner, so that the CPU is always working. Maybe you should know why the memory sticks on the computer motherboard are divided into banks. Obviously, only one bank is inserted slowly into the memory stick will make this method invalid; another method is DRAM Page Mode, that is, dynamic DRAM page mode. The principle is that only one address can be accessed during a cycle when the CPU reads and writes to DRAM. However, if the column address is fixed and only the row address of the memory is changed continuously, a piece of continuous memory (can be called a page) can be obtained, so that the CPU can access a larger range (page) of data, speeding up data access Process. From a single address to multiple addresses, the method from linear to page greatly improves the efficiency of the CPU, and no longer depends on the physical conditions of the BANK. It is not enough to improve the access design method alone. Using new memory materials, improving the triggering of the data read and write cycle

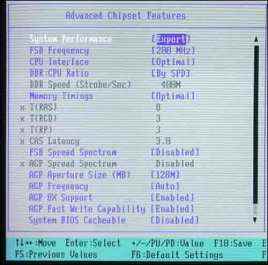

circuits, and more advanced adjustments to the refresh cycle of DRAM in CMOS to optimize the design, etc. can improve the efficiency of the CPU. The good news is the dynamic DRAM. Speed is increasing. The PC133 standard is becoming popular, and PC155 is just around the corner.